Posted by jkula on Sep 02, 2017 in Cray-2, Technical Guides, Modules

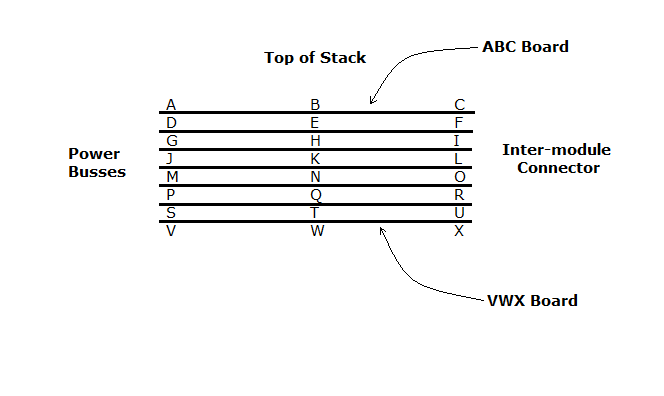

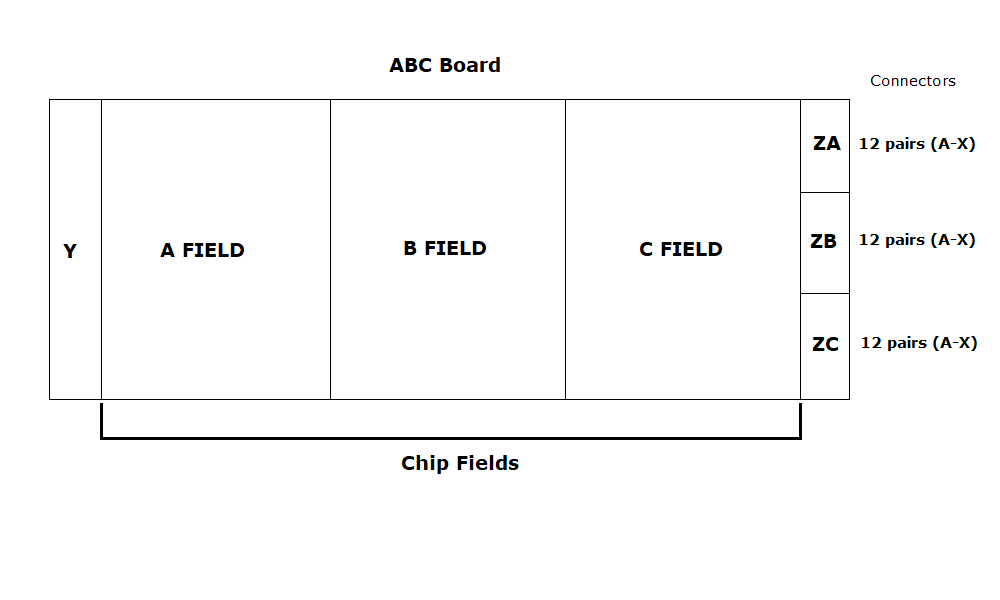

The CRAY-2 was created from a combiation of up to 320 pluggable modules, each module had a specific function within the machine. Below is a complete list of the module names and their description.

| Module Name | Description/Function |

| AM | Address multiply |

| AR | Address registers |

| EA | Foreground processor port |

| EB | Foreground processor port - Channel Function Decodes - Foreground Access Register - Interrupt Address Register - Data Buffer - Length Register - Status Register - Common Memory Error Address - I/O Memory Reference Control - Common Memory Address Register |

| FA | Floating Point Addition |

| FB | Floating Point Addition |

| FC | Floating Point Addition |

| GA |

Scalar Integer Add, Scalar Population Count, and Scalar Leading Zero Count

|

| GB | Scalar shift |

| IE | Instruction buffers |

| IF | Instruction buffers |

| JA | Main issue module |

| JB | Main issue module (CPU issue logic that could not fit on JA) |

| JC | Main issue module - Each JC controls 4 VR modules(each VR is 8 bits of the Vector registers, S registers and some of the vector and Scalar logical operations. There are 2 JC modules.) |

| KA | Foreground CPU |

| KB | Foreground CPU |

| KC | Foreground CPU |

| MA | Floating multiply, reciprocal, reciprocal square root |

| MB | Floating multiply, reciprocal, reciprocal square root |

| MC | Floating multiply, reciprocal, reciprocal square root |

| MD | Floating multiply, reciprocal, reciprocal square root |

| ME | Floating multiply, reciprocal, reciprocal square root |

| Qx* | Memory access control |

| RA | Look up for reciprocal and reciprocal square root |

| Sx* | Memory module |

| TA | Memory interface modules, packetize address and data, SECDED |

| TB | Memory interface modules, packetize address and data, SECDED |

| TC | Memory interface modules, packetize address and data, SECDED |

| TD | Memory interface modules, packetize address and data, SECDED |

| VA | Vector integer adder |

| VB | Vector shift |

| VL | Vector Logical, Real-time counter, vector mask register |

| VR | Scalar Logical, Scaler Register, Vector registers, 8 modules each with 8 bits |

| WA | Local memory |

* Several versions of the Q and S modules were created in order to support a range of memory types and sizes. These ranged from QA-QE, and SA-SF. A specific Qx module

was paired to a specific Sx module, e.g. QB modules drove SB modules.

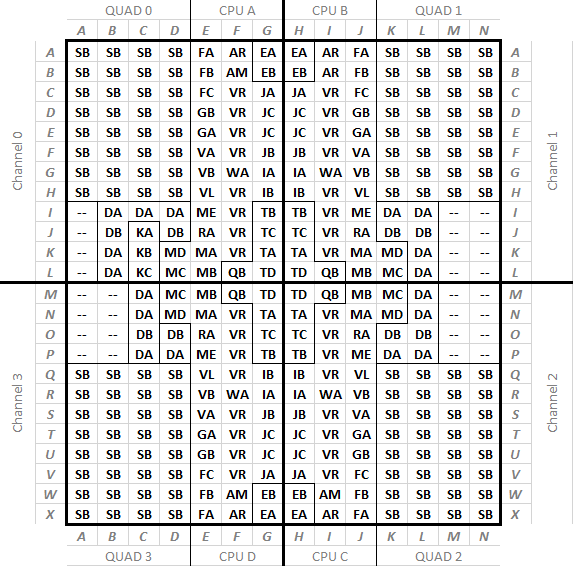

From the above modules a variety of CRAY-2 systems can be assembled. Below is a module layout for a 4-CPU model, in this case serial number 2001.

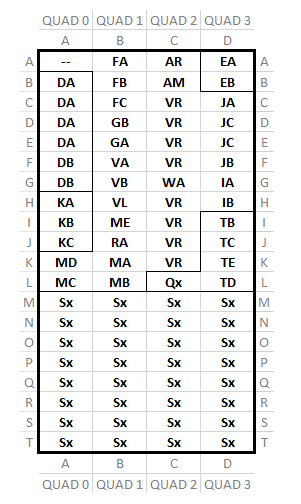

For comparison below is a module layout for a 1-CPU system, this would be a typical layout for the Q1.

Note: This data has never been published publicly, please credit when reposting.